发布于:2024-02-25 12:34:15 来源:产品展示 点击量:14次

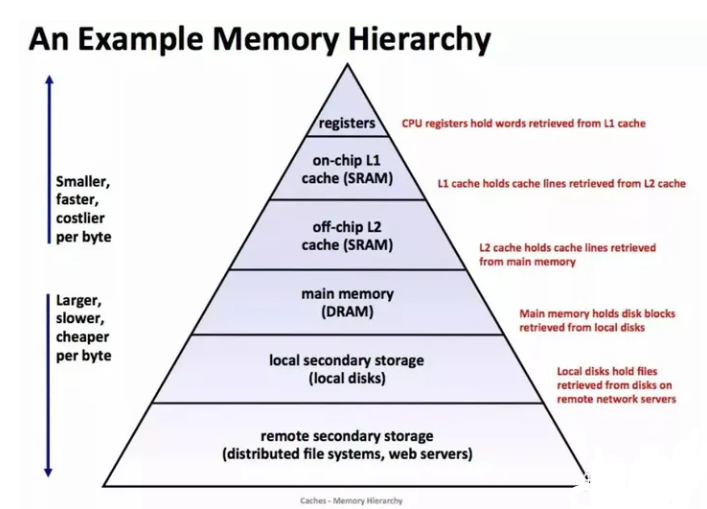

存储器层次结构可以从图片中清晰的看出来,图片分为六级,越向上的层次,存储器速度越快,容量更小,造价越高。

L0层为寄存器,寄存器从硬件的角度来说即触发器( flip-flop ), 通常一个触发器可以由两个锁存器( latcher )和逻辑块组成,触发器为边沿有效,锁存器为电平有效。寄存器集成在CPU内部,制作在CPU内的寄存器不可能容量太大,另一方面实际上CPU并不是特别需要太多的寄存器,寄存器太多反而可能会减慢工作速度。目前的主流的片内寄存器数量为32个(或者64个?)。汇编语言中操作的寄存器也就是指的这些。寄存器由于在片内,避免了线为两级高速缓存( cache ),这两级存储为S

,s即static,指静态,最常见的SRAM为6T结构。高速缓存主要解决CPU计算速度和主存读写速度不匹配的问题,假如没有这两级,有关于内存的读写指令(如load和store)将会极度影响整体速度。高速缓存也一般集成在CPU上。目前主流CPU已经存在3级高速缓存。L3为主存,即我们

中所谓的内存,为DRAM,d即dynamic,即动态,DRAM常见的有1T和3T结构,通过电容存储信号,需要经常刷新不然电荷会漏光。DRAM速度要低于SRAM,但可以明显看出1T只用了6T六分之一的晶体管,节省了六分之一的面积。L4为磁盘内存,也就是我们所说的硬盘。以上的RAM都是掉电失去

的,而硬盘中的内容掉电不会失去。目前机械硬盘主流的存储技术为闪存flash,基于EEPROM。L5层为远端内存,比如

服务器,这些的读写速度主要根据网络延时。为何需要采用这样的分层结构呢?

性能与成本的平衡:不一样的存储器在性能(如访问加载速度)和成本(包括制造成本、功耗等)之间有权衡。高速存储器(如SRAM、Cache)访问加载速度快,但制造成本高、容量小;而低速存储器(如磁盘、RAM)虽然访问加载速度慢,但制造成本低、容量大。通过构建层次结构,可以充分的利用各种存储器的优势,实现性能与成本的平衡。

局部性原理:程序在执行过程中通常会表现出时间局部性和空间局部性。时间局部性指的是程序在某一时刻访问了某个数据后,在不久的将来还可能再一次访问该数据;空间局部性则指的是程序在某一时刻访问了某个数据后,在不久的将来还可能访问其附近的数据。利用这些局部性特性,可以在高速缓存中存放最近访问过的数据和指令,来提升访问加载速度。

减少平均访问时间:通过合理设计各级存储器的容量和访问速度,可以使得大部分数据访问都在高速缓存或主存储器中完成,从而显著减少平均访问时间。

管理复杂性:随技术的发展,存储器的类型和容量都在持续不断的增加。采用层次结构可以简化存储器的管理复杂性,使得系统更容易扩展和升级。

采用存储器层次结构是为了充分的利用各种存储器的优势,实现性能与成本的平衡,同时利用程序的局部性特性来减少平均访问时间,并简化存储器的管理复杂性。这也是现代计算机系统中广泛采用存储器层次结构的原因。

原理 /

原理 当前给定的MCP的概念为:MCP是在一个塑料封装外壳内,垂直堆叠大小不同的各类

(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快的一种RAM基于缓存的

基础知识详细介绍 /

——高速缓存详解 /

麒麟9000S和麒麟9000有什么不同?麒麟9000s和麒麟9000哪个好

STM32F407ZGT6 spi flash片选引脚无法被拉低的原因?如何来解决?

上一篇:数字化企业列表

下一篇:国产大飞机集成数字化环境渠道建成