发布于:2024-06-15 11:33:27 来源:智能制造 点击量:14次

吴锦帆(电子科技大学电子科学与工程学院 四川 成都 610054)

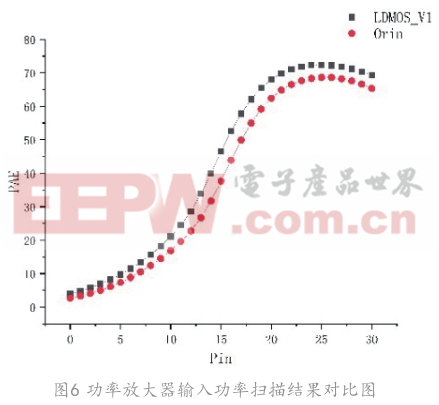

摘 要:本文介绍了一种通过改进LDMOS的器件结构,提升以LDMOS搭建的功率放大器功率附加效率大信号指标的方法。在器件仿真环境中,通过对LDMOS的漂移区进行结构优化,提升器件的小信号增益,然后利用器件等效建模技术,在电路仿真环境中,搭建出功率放大器进行大信号仿真,在相同的工作条件下功率附加效率提升了约5%左右。

横向双扩散金属氧化物半导体场效应管(RFLDMOS)作为一种应用在射频放大器电路中的晶体管,最能体现出其性能的器件参数有输出功率,漏极效率,功率增益等,提高器件的这些参数一直以来是RFLDMOS研究者们的努力的方向,而随着射频终端数量的增加,用户对数据传输速率和容量的要求慢慢的升高,射频电路一直有着向高频率高效率的趋势发展[1]。功率附加效率作为射频功率放大器的大信号指标之一,射频功率放大器具备较高的功率附加效率意味着系统要更小的直流功率供给就可以产生较大的输出功率用于RF信号源的放大。同时也代表着器件在工作的过程中,由于晶体管自身的热阻所产生的热消耗将降低,器件的工作寿命也会相应得延长[2]。因此,功率附加效率的提升不仅意味着输出功率的提升,同时也延长了器件的工作寿命。

针对以上问题,本文提出了一种基于LDMOS器件结构优化的方案,通过大信号与小信号等效模型进行建模的方式,提升以LDMOS作为功率晶体管的射频功率放大器的功率附加效率。文章第2节主要描述该方法的工作原理及流程;第3节给出LDMOS器件结构优化方案;第4节给出等效模型建模方法;第5节给出功率放大器仿线 功率附加效率提升方法原理

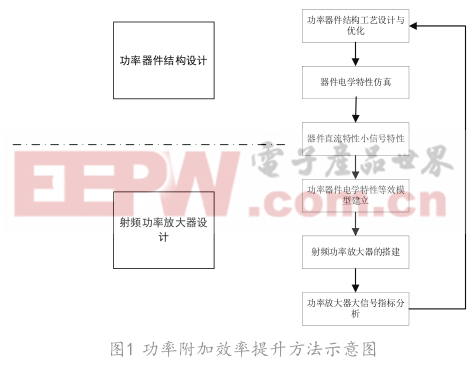

如图1所示,功率附加效率指标提升的方法大致上可以分为两个阶段,功率器件结构设计阶段与射频功率放大器设计阶段。在功率器件设计阶段,利用半导体工艺模拟以及器件模拟工具(TCAD)仿真软件进行器件仿真模型的建立,其中在完成实际工艺与仿真软件参数的校准之后,实现功率器件结构的建模以及器件电学特性的仿真,获得器件的大信号直流特性及交流小信号特性。以器件的直流特性与交流特性作为连接电路仿真与器件仿真的桥梁,通过搭建电学特性等效模型,达到在射频电路仿真环境中功率器件的等效还原的目的。在射频功率放大器设计阶段,利用电路仿真软件,完成射频功率放大器的搭建以及大信号指标的仿真,通过调整电学特性等效模型实现功率放大器大信号指标的优化,并根据电学特性的优化目标指导器件结构设计的优化,最终实现射频功率放大器的功率附加效率的提升。

LDMOS基本结构如图2所示,主要由P_sinker,源极(Source),栅极(Gate),横向漂移区(LDD),漏极(Drain)几个部分所组成,其中通过高能离子注入形成P_sinker将器件的源极与衬底进行了连接,通过背面减薄和背金工艺形成了背面源电极,减少了电极的数量以及衬底与源极的键合连线,降低了寄生的电感与电容,LDD的存在利用RESURF表面电场的原理提升了LDMOS的击穿电压,保证了器件能够在高压RF的用途。而本文中通过将LDD区进行水平分层,分为LDD1,LDD2,其中LDD1为相对低浓度的n掺杂,LDD2维持与原来结构相同的n掺杂浓度,保证了击穿电压与器件导通电阻的不变。低掺杂LDD1的存在降低了右侧沟道与LDD区交界的pn结扩散电容 Cgd

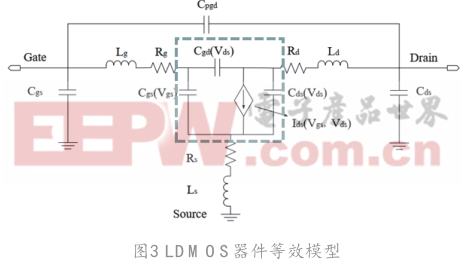

电学特性等效模型如图3所示,其中,小信号等效模型和大信号等效模型结构是一致的,两者不同的地方在于,大信号等效模型的本征部分是时变的,即虚线框内的本征部分受到端口电压的改变而改变,而小信号的等效模型在固定的偏置点和工作频率下是恒定的。

该模型大致上可以分为两部分,其中虚线框内的部分为器件的本征部分,受器件的偏置和工作频率的改变而改变,器件的大信号直流模型表现为一个压控流源,而小信号模型表现为一个恒流源。虚线框外的为器件的寄生参数部分,主要为器件进行封装时产生的电阻和电感以及PAD对地耦合产生的寄生电容,寄生参数部分对偏置和工作频率不敏感

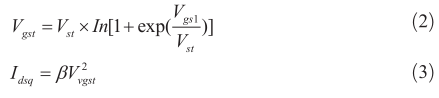

器件的大信号非线性直流特性一般会用非线性经验模型来建模,非线性经验模型是以实验测试数据为基础,通过拟合I-V特性曲线的数据来确定经验模型中公式所需要的参数。将RFLDMOS典型的转移特性曲线,分为四个区:截止区、二次区、线]

在截止区,RFLDMOS器件的漏极电流随栅极电压呈指数变化,此时的漏极电流有如下形式:

为LDMOS的阈值电压, Vst和β的数值根据LDMOS的测试数据来进行拟合得到[5]。RFLDMOS的线性区电流表达式为

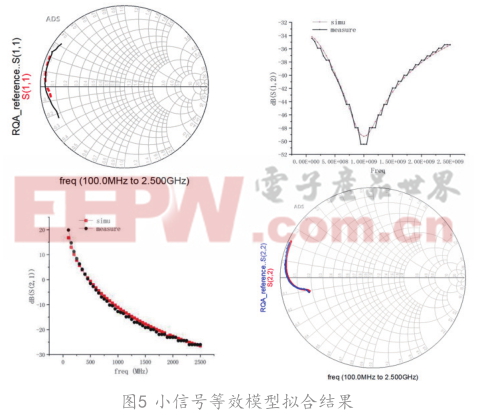

在ADS仿真软件中搭建小信号等效模型,拟合结果如图5所示,小信号模型计算结果与测试数据结果拟合程度良好,该小信号模型基本能表征实际器件的端口特性。

在ADS电路仿真中,将搭建好的LDMOS器件模型进行输入输出匹配,完成功率放大器的搭建,并进行大信号仿线所示,通过器件结构的优化,当小信号模型中的 Cgd降低12%,在相同的匹配电路以及工作偏置条件下,能轻松实现Pout与PAE的整体提升其中,改进后的PAE相比于原来提升5%左右,Pout提升约1 dBm左右。

随着射频终端数量的增加,射频电路一直有着向高频率高效率的趋势发展。在射频功率放大器电路中,功率晶体管作为放大器的核心元件,其端口阻抗及寄生参数不仅影响着放大电路的端口阻抗,电学参数特性的改变不仅会对匹配情况造成改变,也会对功率附件效率、功率增益等大信号特性造成影响。本文介绍了一种通过改进LDMOS器件结构,提升以LDMOS为功率晶体管的功率放大器的功率附加效率的方法,通过对LDMOS器件结构可以进行优化实现了放大器功率附加效率的提升。参考文献:

(注:本文来源于科技期刊《电子科技类产品世界》2020年第06期第xx页,欢迎您写论文时引用,并标注明确出处。)